- 您现在的位置:买卖IC网 > Sheet目录1991 > CS4354-CSZ (Cirrus Logic Inc)IC DAC 24BIT SRL 14SOIC

DS895F2

15

CS4354

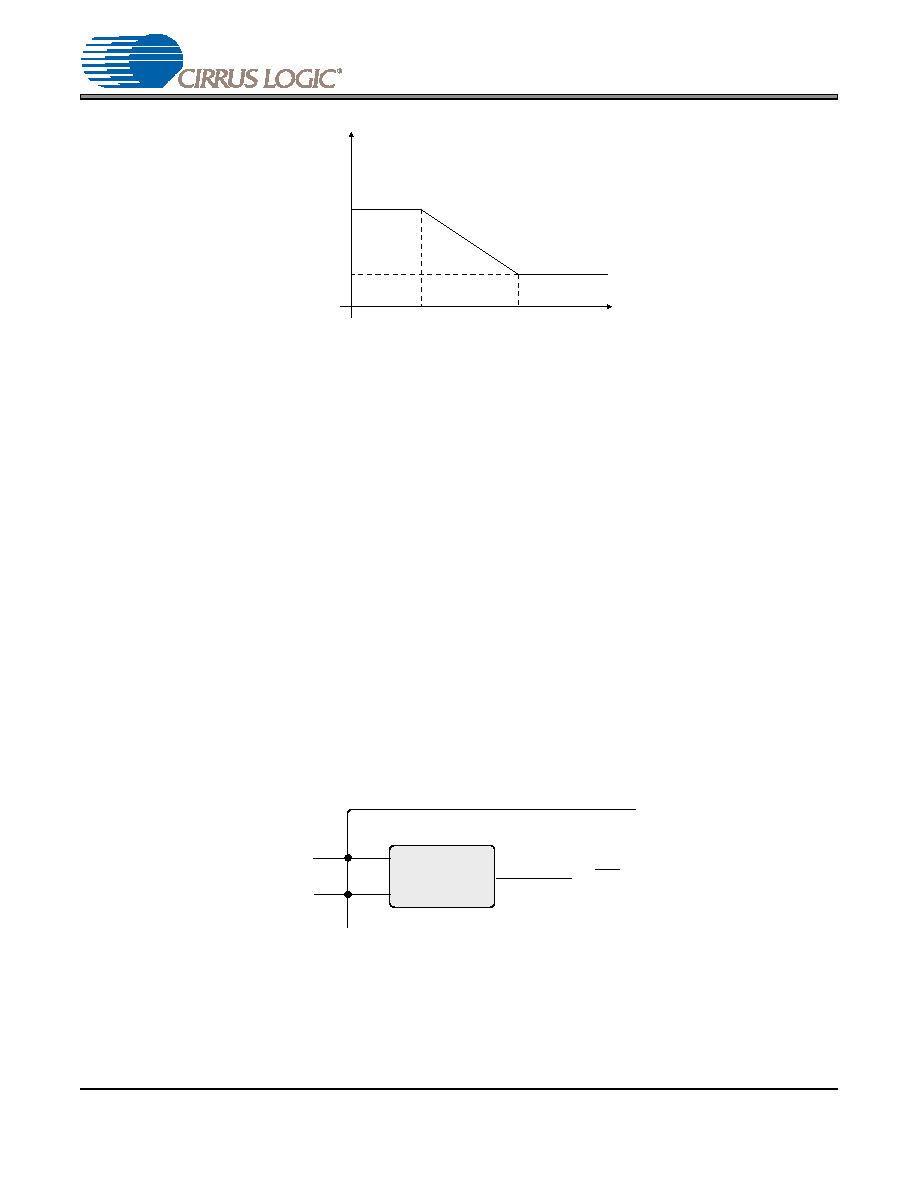

Figure 7. De-Emphasis Curve, Fs = 44.1 kHz

Note:

De-emphasis is only available in Single-Speed Mode.

4.5

Internal High-Pass Filter

The CS4354 includes an internal digital high-pass filter. This filter prevents a constant digital offset from cre-

ating a DC voltage on the analog output pins. The filter’s corner frequency is well below the audio band; see

“Combined Digital and On-Chip Analog Filter Characteristics” on page 7 for filter specifications.

4.6

Digital Interface Format

The device accepts audio samples in the industry standard IS format only.

For an illustration of the required relationship between the LRCK, SCLK and SDIN, see Figure 6 on page

14. SDIN is valid on the rising edge of SCLK. For more information about serial audio formats, refer to Cirrus

Logic Application Note AN282: The 2-Channel Serial Audio Interface: A Tutorial, available at

4.7

Internal Power-On Reset

The CS4354 features an internal power-on reset (POR) circuit. This circuit monitors the VA supply and au-

tomatically asserts or releases an internal reset of the DAC’s digital circuitry when the supply reaches de-

fined thresholds (see “Internal Power-On Reset Threshold Voltages” on page 10). No external clocks are

required for the POR circuit to function.

Figure 8. Internal Power-On Reset Circuit

Gain

dB

-10dB

0dB

Frequency

T2 = 15 s

T1=50 s

F1

F2

3.183 kHz

10.61 kHz

Power-On Reset

Circuit

VA

GND

reset

(internal)

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CS4360-KZZ

IC DAC STER 6CH 102DB 28TSSOP

CS4361-CZZR

IC DAC STER 6CH 105DB 20-TSSOP

CS4362-KQZ

IC DAC 6CH 114DB 192KHZ 48LQFP

CS4362A-DQZ

IC DAC 6CH 114DB 192KHZ 48-LQFP

CS4364-CQZR

IC DAC 103DB 24BIT 6CH 48-LQFP

CS4382A-DQZ

IC DAC 8CH 114DB 192KHZ 48-LQFP

CS4384-CQZR

IC DAC 8CH 103DB 192KHZ 48-LQFP

CS4385-DQZR

IC DAC 8CH 114DB 192KHZ 48-LQFP

相关代理商/技术参数

CS4354-CSZR

制造商:Cirrus Logic 功能描述:5V DAC W/ 2VRMS LINE DRIVER - Tape and Reel 制造商:Cirrus Logic 功能描述:DAC 制造商:Cirrus Logic 功能描述:IC DAC 24BIT SRL 14SOIC

CS4355-CSZ

制造商:Cirrus Logic 功能描述:5-V STEREO DAC WITH 2-VRMS GROUND-CENTERED OUTPUT - Bulk 制造商:Cirrus Logic 功能描述:DAC

CS4355-CSZR

制造商:Cirrus Logic 功能描述:5-V STEREO DAC WITH 2-VRMS GROUND-CENTERED OUTPUT - Tape and Reel 制造商:Cirrus Logic 功能描述:DAC

CS4-36

制造商:SUPERWORLD 制造商全称:Superworld Electronics 功能描述:POWER TRANSFORMER

CS4360

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit, 192 kHz 6 Channel D/A Converter

CS4360_04

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit, 192 kHz 6 Channel D/A Converter

CS4360-BS

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit, 192 kHz 6 Channel D/A Converter

CS4360-BZ

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:24-Bit, 192 kHz 6 Channel D/A Converter